- 您现在的位置:买卖IC网 > Sheet目录1998 > ICS844004AKI-104LFT (IDT, Integrated Device Technology Inc)IC SYNTHESIZER LVDS 32-VFQFPN

ICS844004AKI-104 REVISION A DECEMBER 15, 2010

12

2010 Integrated Device Technology, Inc.

ICS844004I-104 Data Sheet

FEMTOCLOCK CRYSTAL-TO-LVDS FREQUENCY SYNTHESIZER

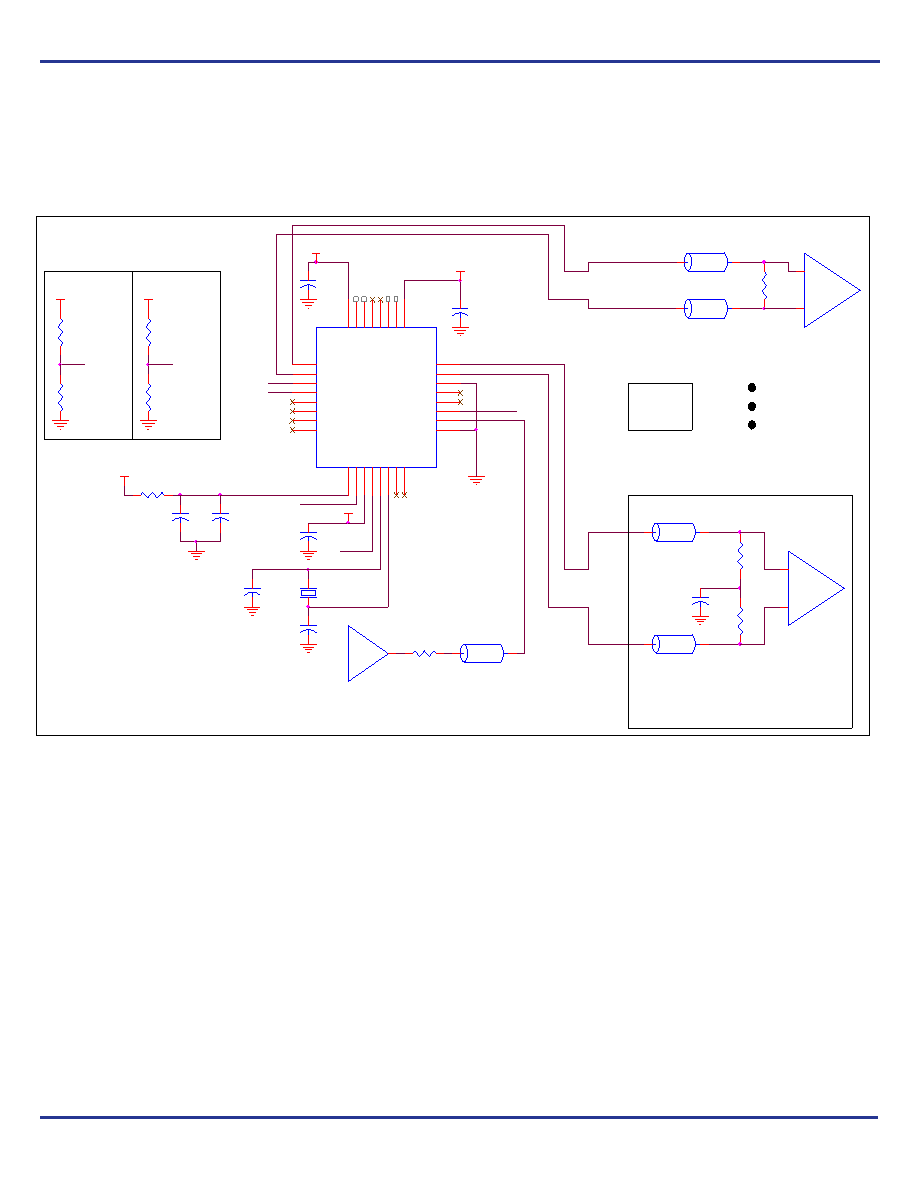

Schematic Example

Figure 6 shows an example of ICS844004I-104 application

schematic. In this example, the device is operated at VDD = VDDO =

3.3V. The 18pF parallel resonant 25MHz crystal is used. The C1 =

33pF and C2 = 27pF are recommended for frequency accuracy. For

different board layouts, the C1 and C2 may be slightly adjusted for

optimizing frequency accuracy. Two examples of LVDS for receiver

without built-in termination are shown in this schematic.

Figure 6. ICS844004I-104 Schematic Layout

R1

33

nQ0

Alternate

LVDS

Termination

C3

0.1uF

nQ

0

R3

50

To Logic

Input

pins

C4

0.1uF

C8

.1uf

nPLL_SEL

Logic Control Input Examples

R2

100

Set Logic

Input to

'1'

VDDA

U1

ICS844004-104

1

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16

17

18

19

20

21

22

23

24

32 31 30 29 28 27 26 25

Q0

nQ0

MR

nPLL_SEL

nc

VD

D

A

F

_

SEL

0

VD

D

F

_

SEL

1

XT

AL

_O

U

T

XT

AL

_I

N

nc nc

GND

REF_CLK

nXTAL_SEL

nc

GND

nQ3

Q3

VD

D

O Q1

nQ

1

nc nc

nQ

2

Q2

VD

D

O

R1

10

VDD=3.3V

RD2

1K

REF_CLK

Zo = 50 Ohm

RU2

Not Install

R4

50

C1

33pF

nQ3

Q3

Zo = 50 Ohm

MR

VDD

nXTAL_SEL

VDD

Q3

Zo = 50 Ohm

nQ3

RD1

Not Install

Zo = 50 Ohm

X1

25MHz

Q1

Driv er_LVCMOS

RU1

1K

F_SEL0

C5

0.01u

To Logic

Input

pins

VDDO

VDD

Q0

C2

27pF

+

-

Set Logic

Input to

'0'

VDDO

+

-

C7

0.1uF

VDD

C6

10uF

F_SEL1

1 8 p F

Q0

VDDO=3.3V

Zo = 50

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS844021BG-01LFT

IC CLOCK GEN ETHERNET 8-TSSOP

ICS844021BGI-01LFT

IC CLOCK GEN ETHERNET 8-TSSOP

ICS844071AGLFT

IC CLOCK GEN GIG ETH 8-TSSOP

ICS844201BG-45LF

IC CLK GENERATOR 25MHZ 8TSSOP

ICS844204BK-245LF

IC CLK SYNTHESIZER 4LVDS 32VFQFN

ICS844S42BKILF

IC SYNTHESIZER RF FREQ 56-VFQFPN

ICS86004BG-01LF

IC CLK BUFFER ZD 1:4 16-TSSOP

ICS8634BY-01LFT

IC BUFFER ZD 1-5 LVPECL 32-LQFP

相关代理商/技术参数

ICS844004BGI-01LF

功能描述:IC SYNTHESIZER 4LVDS 24-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件

ICS844004BGI-01LFT

功能描述:IC SYNTHESIZER 4LVDS 24-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件

ICS844008AKI-46LF

功能描述:IC CLK GEN 8LVDS 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR

ICS844008AKI-46LFT

功能描述:IC CLK GEN 8LVDS 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT

ICS844008AY-16LF

功能描述:IC CLOCK GEN 8LVDS 32PTQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR

ICS844008AY-16LFT

功能描述:IC CLOCK GEN 8LVDS 32PTQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件

ICS844008AYI-01LF

功能描述:IC SYNTHESIZER 8LVDS 32TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件

ICS844008AYI-01LFT

功能描述:IC SYNTHESIZER 8LVDS 32TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件